## ICs for Consumer Electronics

DDC-PLUS-Deflection Controller SDA 9362

#### Edition 1998-02-01

This edition was realized using the software system FrameMaker®

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1998. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

# Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| SDA 9362<br>Revision His                              | story: | Current Version: 1998-02-01                                       |  |  |

|-------------------------------------------------------|--------|-------------------------------------------------------------------|--|--|

| Previous Version:                                     |        | 1997-04-01                                                        |  |  |

| Page (in previous Version)  Page (in current Version) |        | Subjects (major changes since last revision)                      |  |  |

| 30                                                    | 32     | Nom./max. average current and max. standby current specified      |  |  |

| 30 32                                                 |        | Specification of charge current pump of PLL pin LF is unnecessary |  |  |

#### **Data Classification**

#### **Maximum Ratings**

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

#### **Recommended Operating Conditions**

Under this conditions the functions given in the circuit description are fulfilled. Nominal conditions specify mean values expected over the production spread and are the proposed values for interface and application. If not stated otherwise, nominal values will apply at  $T_A$ =25°C and the nominal supply voltage.

#### **Characteristics**

The listed characteristics are ensured over the operating range of the integrated circuit.

#### Edition 1998-02-01

Published by Siemens AG, Semiconductor Group Copyright © Siemens AG 1998. All rights reserved. Terms of delivery and right to change design reserved.

## **SIEMENS**

| Table                                                                             | of Contents                                                                                                                                                                                                       | Page                 |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5                                              | Overview Features General Description Pin Configuration Pin Description Block Diagram                                                                                                                             | 5<br>6<br>6<br>7     |

| 2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.5.5 | System Description Functional Description Circuit Description Reset Modes Frequency Ranges I²C-Bus Control I²C-Bus Address I²C-Bus Format I²C-Bus Commands Detailed Description Explanation of Some Control Items | 10 13 13 14 14 15    |

| <b>3</b><br>3.1<br>3.2                                                            | Absolute Maximum Ratings                                                                                                                                                                                          | 30                   |

| 4                                                                                 | Application Information                                                                                                                                                                                           | 34                   |

| 5<br>5.1<br>5.2<br>5.3<br>5.4                                                     | Waveforms  VD- Output Voltage, 4/3-CRT and 16/9-Source  Function of H,V Protection  Power On/Off Diagram  Standby Mode, RESN Diagram                                                                              | 35<br>36<br>37<br>38 |

| 6                                                                                 | Package Outlines                                                                                                                                                                                                  | 39                   |

## SIEMENS

#### **DDC-PLUS-Deflection Controller**

**SDA 9362**

MOS

#### 1 Overview

#### 1.1 Features

- Deflection Protection 16:9 / 4:3

- I<sup>2</sup>C Bus alignment of all deflection parameters

- All EW-, V- and H-functions (incl.  $\Phi$ 2)

- PW EHT compensation

- PH EHT compensation

- Compensation of H-phase deviation (e.g. caused by white bar)

- Upper/lower EW-corner correction separately adjustable

- V-angle correction: Vertical frequent linear modulation of H-phase

- V-bow correction: Vertical frequent parabolic modulation of H-phase

- Three reduced V-scan modes (75 %, 66 %, 50 % V-size) selectable

- H- and V-blanking time adjustable

- Partial overscan adjustable to hide the cut off control measuring lines in the reduced scan modes

- Stop/start of vertical deflection adjustable to fill out the 16/9 screen with different letterbox formats without annoying overscan

- Dynamic PH EHT-compensation (white bar)

- Self adaptation of V-frequency/number of lines per field between 192 and 680 for each possible line frequency

- Protection against EHT run away (X-rays protection)

- Protection against missing V-deflection (CRT-protection)

- Two digital outputs for general purpose, controlled by I<sup>2</sup>C Bus

- Selectable softstart of the H-output stage

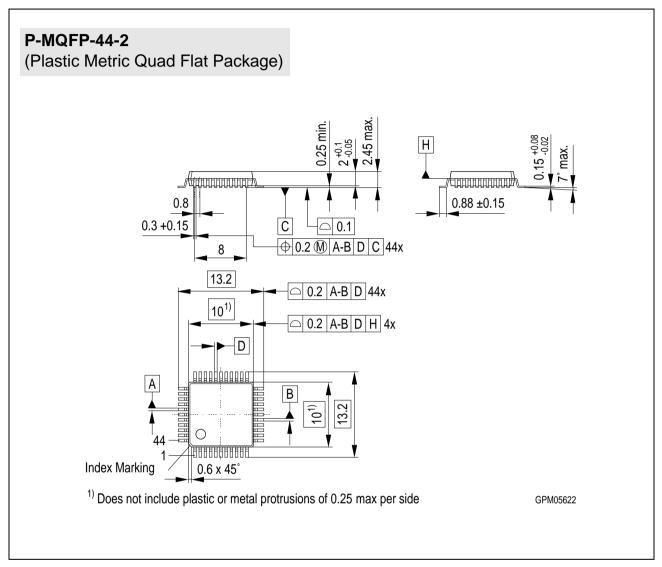

- P-MQFP-44-2 package

- 5 V supply voltage

| Туре     | Ordering Code     | Package     |

|----------|-------------------|-------------|

| SDA 9362 | Q67101-H5173-A701 | P-MQFP-44-2 |

#### 1.2 General Description

The SDA 9362 is a highly integrated deflection controller for CTV receivers with doubled line and standard or doubled field frequencies. It controls among others an horizontal driver circuit for a flyback line output stage, a DC coupled vertical sawtooth output stage and an East-West raster correction circuit. All adjustable output parameters are I<sup>2</sup>C Bus controlled. Inputs are HSYNC, VSYNC and the line locked clock CLL.

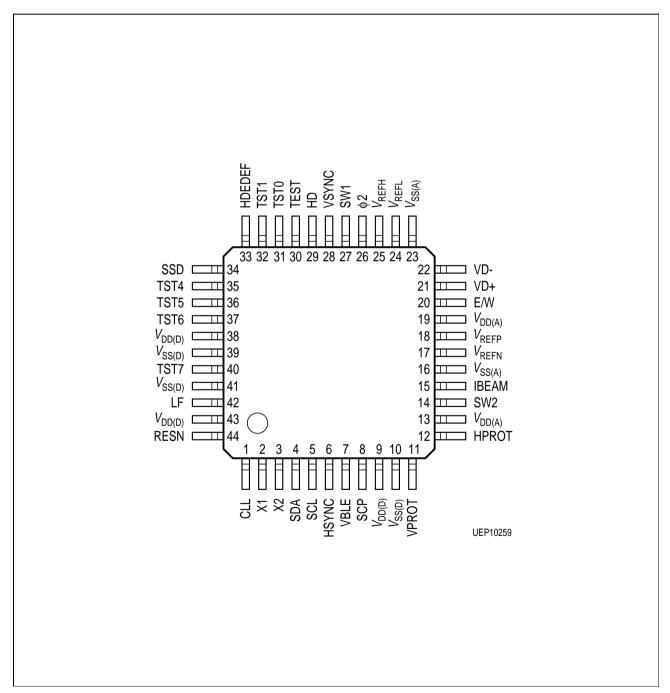

#### 1.3 Pin Configuration

Figure 1

## 1.4 Pin Description

| Pin No. | Symbol      | Туре  | Description                                                                                        |

|---------|-------------|-------|----------------------------------------------------------------------------------------------------|

| 1       | CLL         | I/TTL | Clock input                                                                                        |

| 2       | X1          | I     | Reference oscillator input, crystal                                                                |

| 3       | X2          | Q     | Reference oscillator output, crystal                                                               |

| 4       | SDA         | IQ    | I <sup>2</sup> C-Bus data                                                                          |

| 5       | SCL         | I     | I <sup>2</sup> C-Bus clock                                                                         |

| 6       | HSYNC       | I/TTL | H-sync input                                                                                       |

| 7       | VBLE        | Q/TTL | Vertical blanking output                                                                           |

| 8       | SCP         | Q     | Blanking signal with H- and color burst component (V-component selectable by I <sup>2</sup> C Bus) |

| 9       | $V_{DD(D)}$ | S     | Digital supply                                                                                     |

| 10      | $V_{SS(D)}$ | S     | Digital ground                                                                                     |

| 11      | VPROT       | I     | Watching external V-output stage (input is the V-sawtooth from feedback resistor)                  |

| 12      | HPROT       | I     | Watching EHT (input is e.g. H-flyback)                                                             |

| 13      | $V_{DD(A)}$ | S     | Analog supply                                                                                      |

| 14      | SW2         | Q/TTL | Output of an I <sup>2</sup> C Bus controlled switch (Register 00 <sub>H</sub> , Bit D5)            |

| 15      | IBEAM       | I     | Input for a beam current dependent signal for stabilization of width, height and H-phase           |

| 16      | $V_{SS(A)}$ | S     | Analog ground                                                                                      |

| 17      | $V_{REFN}$  | IQ    | Ground for $V_{REFP}$ , $V_{REFH}$ , $V_{REFL}$                                                    |

| 18      | $V_{REFP}$  | IQ    | Reference voltage for IBEAM ADC, HPROT / VPROT thresholds                                          |

| 19      | $V_{DD(A)}$ | S     | Analog supply                                                                                      |

| 20      | E/W         | Q     | Control signal output for East-West raster correction                                              |

| 21      | VD+         | Q     | Control signal output for DC coupled V-output stage                                                |

| 22      | VD-         | Q     | Like VD+                                                                                           |

| 23      | $V_{SS(A)}$ | S     | Analog ground                                                                                      |

| 24      | $V_{REFL}$  | IQ    | Reference voltages for E/W-DAC, V-DAC                                                              |

| 25      | $V_{REFH}$  | IQ    | Like $V_{REFL}$                                                                                    |

| 26      | Ф2          | I     | Line flyback for H-delay compensation                                                              |

## 1.4 Pin Description (cont'd)

| Pin No. | Symbol          | Туре  | Description                                                                                      |

|---------|-----------------|-------|--------------------------------------------------------------------------------------------------|

| 27      | SW1             | Q/TTL | Output of an I <sup>2</sup> C Bus controlled switch (Register 00 <sub>H</sub> , Bit D3)          |

| 28      | VSYNC           | I/TTL | V-sync input                                                                                     |

| 29      | HD              | Q     | Control signal output for H driver stage                                                         |

| 30      | TEST            | I/TTL | Switching normal operation (TEST = L) and test mode (TEST = H: pin 34 is an additional test pin) |

| 31      | TST0            | I     | Test pin, to be grounded                                                                         |

| 32      | TST1            | I     | Test pin, to be grounded                                                                         |

| 33      | HDEDEF          | I/TTL | Defines the default value of HDE                                                                 |

| 34      | SSD             | I/TTL | Disables soft start (H)                                                                          |

| 35      | TST4            | I     | Test pin, to be grounded                                                                         |

| 36      | TST5            | 0     | Test pin, don't connect                                                                          |

| 37      | TST6            | 0     | Test pin, don't connect                                                                          |

| 38      | $V_{DD(D)}$     | S     | Digital supply                                                                                   |

| 39      | $V_{\rm SS(D)}$ | S     | Digital ground                                                                                   |

| 40      | TST7            | 0     | Test pin, don't connect                                                                          |

| 41      | $V_{\rm SS(D)}$ | S     | Digital ground                                                                                   |

| 42      | LF              | IQ    | PLL loop filter                                                                                  |

| 43      | $V_{DD(D)}$     | S     | Digital supply                                                                                   |

| 44      | RESN            | I/TTL | Reset input, active low                                                                          |

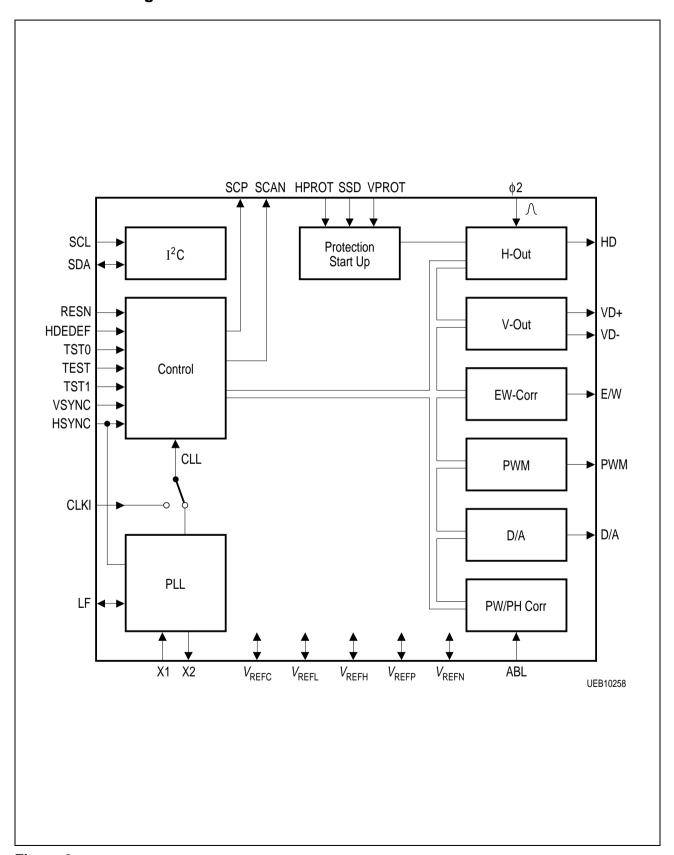

## 1.5 Block Diagram

Figure 2

#### 2 System Description

#### 2.1 Functional Description

The main input signals are HSYNC with doubled horizontal frequency, VSYNC with vertical frequencies of 50/100 Hz or 60/120 Hz and the line locked clock CLL.

The output signals control the horizontal as well as the vertical deflection stages and the East-West raster correction circuit.

The H-output signal HD compensates the delays of the line output stage and its phase can be modulated vertical frequent to remove horizontal distortions of vertical raster lines (V-Bow, V-Angle). Time reference is the middle of the front and back edge of the line flyback pulse. A positive HD pulse switches off the line output transistor. Maximal H-shift is  $2.25~\mu s$ .

Picture tubes with 4:3 or 16:9 aspect ratio can be used by adapting the raster to the aspect ratio of the source signal.

The V-output sawtooth signals VD- and VD+ controls a DC coupled output stage and can be disabled. Suitable blanking signals are delivered by the IC.

The East-West output signal E/W is a vertical frequent parabola of 4th order, enabling an additional corner correction, separately for the upper and lower part.

Two I<sup>2</sup>C Bus controlled digital outputs are available for general purpose.

The picture width and picture height compensation (PW/PH Comp) processes the beam current dependent input signal IBEAM with effect to the outputs E/W and VD to keep width and height constant and independent of brightness.

The alignment parameter Horizontal Shift Compensation enables to adjust the influence of the input signal IBEAM on the horizontal phase.

The selectable start up circuit controls the energy supply of the H-output stage during the receiver's run up time by smooth decreasing the line output transistors switching frequency down to the normal operating value (softstart). HD starts with about 55 kHz and converges within 85 ms to its final value. The high time is kept constant. The normal operating pulse ratio H/L is 45/55. A watch dog function limits the period of the HD output signal independent of the clock CLL to max 35.2  $\mu$ s.

The protection circuit watches an EHT reference and the sawtooth of the vertical output stage. H-output stage is switched off if the EHT succeeds a defined threshold or if the V-deflection fails (**refer to page 36**). The function of this circuit is based on the internal quartz oscillator and therefore independent of the input clock CLL.

HPROT: Input  $V_i < V2$  Continues blanking

$V_i > V1$  HD disabled  $V2 \le V_i < V1$  Operating range

VPROT: Vertical sawtooth voltage

$V_i$  < V1 in first half of V-period or  $V_i$  > V2 in second half: HD disabled

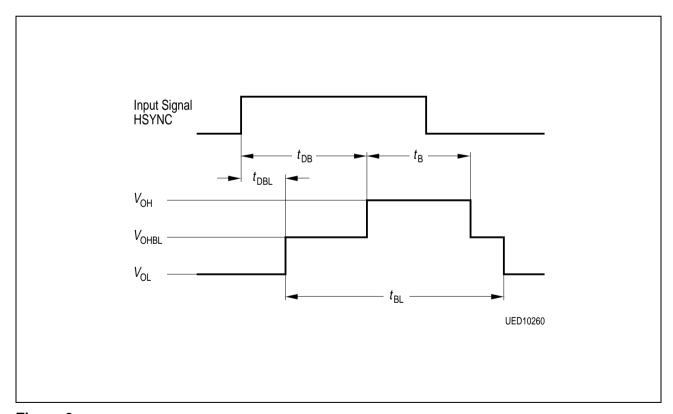

The pin SCP delivers the composite blanking signal SCP. It contains burst ( $V_b$ ), H-blanking HBL ( $V_{HBL}$ ) and selectable V-blanking (control bit SSC). The phase of the H-blanking period can be varied by I<sup>2</sup>C Bus. For the timing following settings are possible:

BD = 1 :  $t_{BL} = 0$

BD = 0, BSE = 0 (default value) :  $t_{HBL} = t_f$  (H-flyback time)

BD = 0, BSE = 1(alignment range) :  $t_{HBL} = (4 * H-blanking-time + 1) / CLL$

:  $t_{DBL}$  = (H-shift + 4 \* H-blanking-phase

-2 \* H-blanking-time + 43) / CLL

SSC = 0:  $t_{BL} = t_{VBL}$  during V-blanking period

$SSC = 1 : t_{BL} is always t_{HBL}$

Figure 3

BG-pulse width  $t_{\rm B}$  54 / CLL Delay to HSYNC  $t_{\rm DB}$  36 / CLL

#### 2.2 Circuit Description

The system clock for the SDA 9362 has to be generated externally (e.g. in the SDA 9206) and applied to pin CLL. Its frequency must be always the line frequency (defined by the horizontal time reference HSYNC) multiplied by 864. If no HSYNC signal is available an internal horizontal synchronisation signal is derived from CLL (CLL divided by 879).

The input signal at VSYNC is the vertical time reference. It has to pass a window avoiding too short or long V-periods in the case of distorted or missing VSYNC pulses. The window allows a VSYNC pulse only after a minimum number of lines from its predecessor and sets an artificial one after a maximum number of lines. The window size is programmable by I<sup>2</sup>C Bus.

The beam current dependent input signal IBEAM is A/D converted and then digitally processed. The A/D Converter requires a clock frequency twice the frequency of CLL which is generated by an internal analog PLL with an external loop filter at pin LF.

Values which influence shape and amplitude of the output signals are transmitted as reduced binary values to the SDA 9362 via I<sup>2</sup>C Bus. A CPU which is designed for speed reasons in a pipe line structure calculates in consideration of feedback signals (e.g. IBEAM) values which exactly represent the output signals. These values control after D/A conversion the external deflection and raster correction circuits. The CPU firmware is stored in an internal ROM.

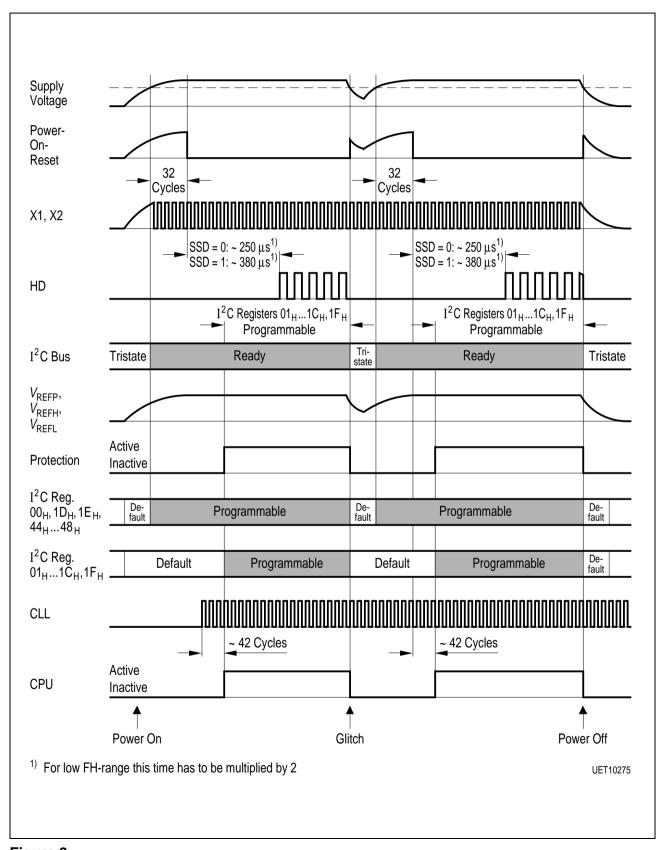

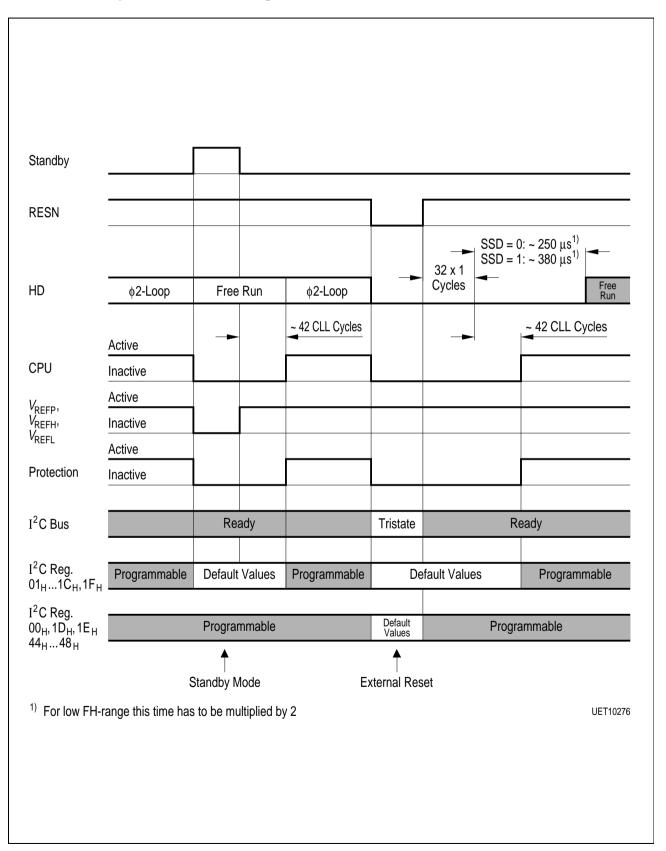

#### 2.3 Reset Modes

The circuit is only completely reset at power-on/off (**timing diagram refer 5.3**). If the pin RESN has L-level or during standby operation some parts of the circuit are not affected (**timing diagram refer 5.4**):

|                                                                | Power-On-Reset         | External Reset (pin RESN=0) | Standby Mode<br>(I <sup>2</sup> C-Bit STDBY=1) |

|----------------------------------------------------------------|------------------------|-----------------------------|------------------------------------------------|

| HD output                                                      | High                   | Active                      | Active                                         |

| H-protection                                                   | Inactive               | Active                      | Active                                         |

| V-protection                                                   | Inactive               | Active <sup>1)</sup>        | Active <sup>1)</sup>                           |

| I <sup>2</sup> C Interface (SDA, SCL)                          | Tristate               | Ready                       | Ready                                          |

| I <sup>2</sup> C Register<br>01 <sub>H</sub> 1B <sub>H</sub>   | Set to default values  | Set to default values       | Set to default values                          |

| I <sup>2</sup> C Register<br>00 <sub>H</sub> , 48 <sub>H</sub> | Set to default values  | Not affected                | Not affected                                   |

| Status bit PONRES                                              | Set to 1 <sup>2)</sup> | Set to 1                    | Not affected                                   |

| $\overline{V_{REFP}}$                                          | Not affected           | Not affected                | Not affected                                   |

| $\overline{V_{REFH},V_{REFL}}$                                 | Not affected           | Not affected                | Inactive                                       |

| CPU                                                            | Inactive               | Inactive                    | Inactive                                       |

<sup>1)</sup> Inactive if HPROT < V2 (typ. 2.4 V)

**Note:** Power-On-Reset state is deactivated after ca. 32 cycles of the X1/X2 oscillator clock. RESN = Low and standby state are deactivated after ca. 42 cycles of the CLL clock.

#### 2.4 Frequency Ranges

| Н         | V               | $n_L$                    |

|-----------|-----------------|--------------------------|

| 31.25 kHz | 50 Hz<br>100 Hz | 625 NI / 1250I<br>625 I  |

| 31.5 kHz  | 60 Hz<br>120 Hz | 525 NI / 1050 I<br>525 I |

The allowed deviation of all input line frequencies is max. ±4.5 %.

n<sub>L</sub>: Number of lines per frame

I: Interlaced

NI: Non interlaced

<sup>2)</sup> Can only be read after Power-On-Reset is finished

If NSA = 0 (subaddress  $01_H/D5_H$ ) number of lines per field is selfadaptable between 192 and 680 for each specified H-frequency.

#### 2.5 I<sup>2</sup>C-Bus Control

#### 2.5.1 I<sup>2</sup>C-Bus Address

| 1 | 0 | 0 | 0 | 1 | 1 | 0 |

|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|

#### 2.5.2 I<sup>2</sup>C-Bus Format

write:

| 3  | S     | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | Α | Subaddress  | Α | Data Byte   | Α | **** | Α  | Р |

|----|-------|---|---|---|---|---|---|---|---|---|-------------|---|-------------|---|------|----|---|

| re | read: |   |   |   |   |   |   |   |   |   |             |   |             |   |      |    |   |

| 3  | S     | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | Α | Status byte | Α | Data Byte n | Α | **** | NA | Р |

Reading starts at the last write address n. Specification of a subaddress in reading mode is not possible.

S: Start condition

A: Acknowledge

P: Stop condition

NA: Not acknowledge

An automatical address increment function is implemented.

After switching on the IC, all bits are set to defined states  $(00_{H})$  (exception: HDE depends on pin 33; see page 17)

## 2.5.3 I<sup>2</sup>C-Bus Commands

| Control Item                   | Sub-<br>addr.   | D7 | D6 | D5 | D4   | D3    | D2 | D1 | D0 | Allowed<br>Range | Effective<br>Range | Can be<br>Disabled<br>by Bit | Default<br>Value if<br>Disabled | Unit       |

|--------------------------------|-----------------|----|----|----|------|-------|----|----|----|------------------|--------------------|------------------------------|---------------------------------|------------|

| Deflection control 0           | 00 <sub>H</sub> |    |    | S  | ee b | oelov | N  |    |    | _                | _                  | _                            | _                               | _          |

| Deflection control 1           | 01 <sub>H</sub> |    |    | S  | ee b | oelov | N  |    |    | _                | _                  | _                            | _                               | _          |

| Vertical shift                 | 02 <sub>H</sub> | В7 | B6 | B5 | B4   | В3    | B2 | B1 | B0 | -128127          | -128127            | _                            | -                               | _          |

| Vertical size                  | 03 <sub>H</sub> | В7 | B6 | B5 | B4   | ВЗ    | B2 | B1 | B0 | -128127          | -128127            | -                            | _                               | _          |

| Vertical linearity             | 04 <sub>H</sub> | В7 | В6 | B5 | В4   | ВЗ    | B2 | B1 | B0 | -128127          | -128127            | _                            | _                               | _          |

| Vertical S-correction          | 05 <sub>H</sub> | В7 | В6 | B5 | B4   | В3    | B2 | B1 | B0 | -128127          | -128127            | _                            | _                               | _          |

| Vertical EHT compensation 1)   | 06 <sub>H</sub> | В7 | B6 | B5 | B4   | ВЗ    | B2 | B1 | B0 | -128127          | -128127            | _                            | _                               | _          |

| Horizontal size                | 07 <sub>H</sub> | В7 | В6 | B5 | В4   | ВЗ    | B2 | B1 | B0 | -128127          | -128127            | _                            | _                               | _          |

| Pin phase                      | 08 <sub>H</sub> | В7 | В6 | B5 | В4   | ВЗ    | B2 | B1 | B0 | -128127          | -128127            | _                            | _                               | _          |

| Pin amp                        | 09 <sub>H</sub> | В7 | В6 | B5 | В4   | ВЗ    | B2 | B1 | B0 | -128127          | -128127            | _                            | _                               | _          |

| Upper corner pin correction    | 0A <sub>H</sub> | В7 | B6 | B5 | B4   | ВЗ    | B2 | B1 | B0 | -128127          | -128127            | ı                            | _                               | _          |

| Lower corner pin correction    | 0B <sub>H</sub> | В7 | B6 | B5 | B4   | ВЗ    | B2 | B1 | B0 | -128127          | -128127            | -                            | _                               | _          |

| Horizontal EHT compensation 1) | 0C <sub>H</sub> | В7 | B6 | B5 | B4   | ВЗ    | B2 | B1 | B0 | -128127          | -128127            | -                            | _                               | _          |

| Horizontal shift               | 0D <sub>H</sub> | B6 | B5 | B4 | ВЗ   | B2    | B1 | B0 | Χ  | -6463            | -6463              | I                            | _                               | 1/CLL      |

| Vertical angle                 |                 |    |    |    |      |       |    |    |    | -128127          | -128127            | -                            | _                               | _          |

| Vertical bow                   | 0F <sub>H</sub> | B7 | B6 | B5 | B4   | ВЗ    | B2 | B1 | B0 | -128127          | -128127            | -                            | _                               | _          |

| Vertical blanking time 1)      | 10 <sub>H</sub> | Χ  | B6 | B5 | B4   | ВЗ    | B2 | B1 | B0 | 0127             | a)                 | BSE = 0                      | b)                              | lines      |

| Horizontal blanking time       | 11 <sub>H</sub> | Χ  | Χ  | B5 | B4   | ВЗ    | B2 | B1 | B0 | 063              | 063                | BSE = 0                      | H-flyback                       | 4/CLL      |

| Horizontal blanking phase      | 12 <sub>H</sub> | B5 | B4 | ВЗ | B2   | B1    | В0 | Χ  | Χ  | -3231            | -3231              | -                            | _                               | 4/CLL      |

| Start vertical scan 1)         | 13 <sub>H</sub> | B7 | B6 | B5 | B4   | ВЗ    | B2 | B1 | B0 | -128127          | c)                 | SSE = 0                      | 9                               | line       |

| Vertical scan width 0 1)       | 14 <sub>H</sub> | Χ  | Χ  | Χ  | Χ    | Χ     | Χ  | B9 | B8 | 03               | d)                 | STE = 0                      | e)                              | 256 lines  |

| Vertical scan width 1 1)       | 15 <sub>H</sub> | B7 | B6 | B5 | B4   | ВЗ    | B2 | B1 | B0 | 0255             | d)                 | STE = 0                      | e)                              | lines      |

| Guard band 1)                  | 16 <sub>H</sub> | Χ  | Χ  | B5 | В4   | ВЗ    | B2 | B1 | B0 | 063              | 063                | GBE = 0                      | 3                               | half lines |

| Start reduced scan 1)          | 17 <sub>H</sub> | X  | Χ  | B5 | B4   | ВЗ    | B2 | B1 | B0 | 063              | 0, 263             | SRSE = 0                     | 2                               | line       |

| Vertical sync control          | 18 <sub>H</sub> |    |    | S  | ee b | elov  | N  |    |    | _                | _                  | _                            | -                               | _          |

| MinNo. of lines / field 1)     | 19 <sub>H</sub> | В7 | B6 | B5 | B4   | ВЗ    | B2 | B1 | В0 | 0255             | 0255               | _                            | -                               | 2 lines    |

| Max. No. of lines / field 1)   | 1A <sub>H</sub> | В7 | B6 | B5 | B4   | ВЗ    | B2 | B1 | В0 | 0255             | 0255               |                              | _                               | 2 lines    |

| AFC EHT compensation 1)        | 1B <sub>H</sub> | B5 | B4 | В3 | B2   | B1    | B0 | X  | Х  | -3231            | -3231              | _                            | _                               | _          |

| Internal voltage Ref control   | 48 <sub>H</sub> |    |    | S  | ee b | oelov | N  |    |    | ı                | _                  | 1                            | _                               | _          |

<sup>1)</sup> see 2.5.5: Explanation of some control items

a) The effective range for Vertical Blanking Time:

16 ... 127 (absolute value) if STE = 0 0 ... 127 (offset value) if STE = 1.

b) The "default value if disabled" for Vertical Blanking Time:

21 (absolute value) if STE = 0 8 (offset value) if STE = 1.

c) The effective range for **Start Vertical Scan**:

2 ... 127 (absolute value) if STE = 0 if STE = 1 and NSA = 1 -128 ... 127 (offset value) if STE = 1 and NSA = 0.

- d) The effective range for Vertical Scan (total width: 10 Bit): 160 ... 684 lines.

- e) The "default value if disabled" for **Vertical Scan** equals the number of lines of the source signal reduced by the control value for **Start Vertical Scan**. (E.g.: input signal: 262 lines per field; Start vertical scan = 8 lines; then (if SSE = 1, STE = 0) vertical scan = 262 8 = 254 lines.

At power on the RAM containing the control items is cleared. Therefore all data are zero by default before transferring individual values via I<sup>2</sup>C Bus.

Allowed values out of the effective range are limited, e. g. Vertical blanking time = 3 is limited to 16 if STE = 0 (that means a minimum of 16 lines is blanked).

There are five bits (SRSE, BSE, SSE, STE, GBE) in the deflection control byte 1 for disabling some control items. If one of these bits is "0", the value of the corresponding control item will be ignored and replaced by the value "default value if disabled" in the table above.

## 2.5.4 Detailed Description

The **Deflection Control Byte 0** includes the following bits:

| VOFF STDBY SW2 | BD SW1 | VR1 | VR0 | HDE | 1 |

|----------------|--------|-----|-----|-----|---|

|----------------|--------|-----|-----|-----|---|

VOFF: Vertical off

0: normal vertical output due to control items

vertical saw-tooth is switched off, vertical protection is disabled

STDBY: Stand-by mode

0: normal operation

1: stand-by mode (all internal clocks are disabled)

SW2: Setting of output SW2

0: output SW2 has L-level1: output SW2 has H-level

BD: Blanking disable

0: horizontal and vertical blanking enabled1: horizontal and vertical blanking disabled

SW1: Setting of output SW1

0: output SW1 has L-level1: output SW1 has H-level

VR1 ... VR0: Reduction of vertical size

00: 100 % V-size (16:9 source on 16:9 display)

01: 75 % V-size (16:9 source on 4:3 display)

10: 66 % V-size (two 4:3 sources on 16:9 display)

11: 50 % V-size (two 16:9 sources on 16:9 display)

HDE: HD enable

0: line is switched off (HD disabled, that is H-level)

1: line is switched on (HD enabled)

Default value depends on pin 33 (HDEDEF):

HDEDEF = Low: 0 HDEDEF = High: 1

## The **Deflection Control Byte 1** includes the following bits:

| X | VDC | NSA | STE | GBE | SRSE | SSE | BSE |  |

|---|-----|-----|-----|-----|------|-----|-----|--|

|---|-----|-----|-----|-----|------|-----|-----|--|

VDC: Vertical dynamic compensation

0: influence of the beam current input IBEAM on the vertical sawtooth is static ('zooming' correction)

1: influence of the beam current input IBEAM on the vertical sawtooth is dynamic ('ripple' correction)

NSA: No self adaptation

0: self adaptation on1: self adaptation off

STE: Scan time enable

0: control items for vertical scan width 0 and width 1 are disabled1: control items for vertical scan width 0 and width 1 are enabled

GBE: Guard band enable

0: control item for guard band is disabled1: control item for guard band is enabled

SRSE: Start reduced scan enable

0: control item for start reduced scan is disabled1: control item for start reduced scan is enabled

SSE: Start scan enable

0: control item for start vertical scan is disabled1: control item for start vertical scan is enabled

BSE: Blanking select enable

0: control items for blanking times are disabled1: control items for blanking times are enabled

## The Vertical Sync Control Byte includes the following bits:

| X VBLE SSC | Х | NI | Х | Х | Х |

|------------|---|----|---|---|---|

|------------|---|----|---|---|---|

VBLE: Vertical blanking extension

(this bit does not change the VBL component at output SCP, only the

trailing edge of VBLE is affected)

0: output VBLE has the same timing as VBL component at SCP1: output VBLE is 6 lines longer than VBL component at SCP

SSC: Sandcastle without VBL

0: output SCP with VBL component1: output SCP without VBL component

NI: Non interlace

0: interlace depends on source

1: no interlace

#### The Internal Voltage Ref Control Byte includes the following bits:

| BANDG5 | BANDG4 | BANDG3 | BANDG2 | BANDG1 | BANDG0 | BANDG | BANDG4 |

|--------|--------|--------|--------|--------|--------|-------|--------|

|        |        |        |        |        |        | OFF   | OFF    |

BANDG5 ... Adjustment of internal bandgap reference

BANDG0:100000: Reference Output voltage min

:

011111: Reference Output voltage max

Typical adjustment range is 1 V.

BANDGOFF: Bandgap off

0:  $V_{REFH}$ ,  $V_{REFE}$  derived internally from  $V_{REFE}$

1: external references on  $V_{\mathsf{REFP}}$ ,  $V_{\mathsf{REFH}}$ ,  $V_{\mathsf{REFL}}$  have to be applied

(in this case BANDG4OFF must be = 1)

BANDG4OFF: Bandgap 4 V off

0: internal bandgap reference is used for  $V_{REFP}$

1: external reference on  $V_{REFP}$  (4 V) has to be applied

## The Status Byte includes the following bits

| HPON | VPON | _ | _ | _ | _ | _ | PONRES |

|------|------|---|---|---|---|---|--------|

| _    | _    |   |   |   |   |   | _      |

HPON: H-protection on

0: normal operation of the line output stage

1: high level on input HPROT has switched off the line

VPON: V-protection on

0: normal operation of the vertical output stage

1: incorrect signal on input VPROT has switched off the line

PONRES: Power On Reset

0: after bus master has read the status byte

1: after each detected reset

Note: PONRES is reset after this byte has been read.

#### 2.5.5 Explanation of Some Control Items

#### Start Vertical Scan

If enabled (SSE = 1) this control item defines the start of calculation of the vertical sawtooth, the east/west parabola and the vertical function required for the vertical modulated output HD.

#### Vertical Scan (width0 and width1)

The total width of this control item is 10 Bit. Therefore two (width0 and width1) registers are necessary. If enabled (STE = 1) it defines the duration of the vertical scan. When the vertical period has more lines than the sum of **Start Vertical Scan** and **Vertical Scan**, the calculation of the vertical sawtooth, the east/west parabola and the vertical parabola required for HD stops so that the corresponding output signals remain unchanged till the next vertical synchron pulse.

#### **Guard Band**

This control item is useful for optimizing self adaptation. Video signals with different number of lines in consecutive fields (e. g. VCR search mode) must not start the procedure of self adaptation. But switching between different TV standards has to change the slope of the vertical sawtooth getting always the same amplitude (self adaptation).

To avoid problems with flicker free TV systems which have alternating number of lines per field an average value of four consecutive fields is calculated. If the deviation of these average values (e.g. PAL: 312.5 lines or 625 half lines) is less or equals **Guard Band**, no adaptation takes place. When it exceeds **Guard Band**, the vertical slope will be changed.

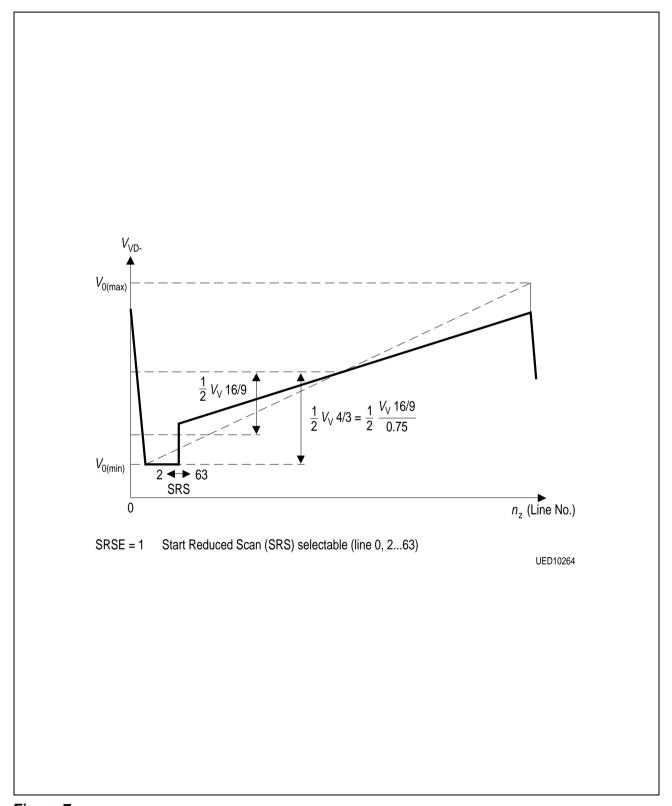

#### Start Reduced Scan

If enabled (SRSE = 1) this item defines the start of the D/A-conversion of the calculated vertical sawtooth. From begin of the vertical flyback to the line defined by **Start Reduced Scan** the output signals VD+, VD- remain unchanged (flyback level). Other outputs are not affected.

a) control bits VR1, VR0 # 00 (reduction of vertical size)

In this case the byte is useful for e.g. displaying 16/9 source format on 4/3 picture tubes without visible RGB lines generated of the automatic cut-off control (partial

overscan). It defines the start of the reduced amplitude (factors 0.5, 0.66, 0.75) of the vertical sawtooth (**refer page 35**). When **Start Reduced Scan** = 0 the reduction takes place over all lines including vertical flyback.

b) control bits VR1, VR0 = 00 (no reduction of vertical size) If Start Reduced Scan > Start Vertical Scan the D/A conversion of the sawtooth starts (Start Reduced Scan - Start Vertical Scan) lines after begin of the calculation.

This causes a jump of the output voltage VD+, VD- from flyback to scan level. It may be useful to hide the automatic cut-off control lines if no overscan is desired (e.g. for VGA display). If **Start Reduced Scan** <= **Start Vertical Scan** this byte has no effect.

#### **Vertical EHT Compensation**

This item controls the influence of the beam current dependent input signal IBEAM on the outputs VD+ and VD- according to the following equation

$$\Delta V_{\text{VDPP}} = \Delta V_{\text{IBEAM}} * \frac{\text{Vertical EHT compensation} + 128}{512} * 0.57^{1)}$$

$\Delta V_{\text{VDPP}}$ : variation of VD+ and VD- peak-to-peak voltage

$\Delta V_{\mathsf{IBEAM}}$ : variation of IBEAM input voltage

<sup>1)</sup> the factor 0.57 depends on  $V_{\mathsf{REFP}}$ ,  $V_{\mathsf{REFH}}$ ,  $V_{\mathsf{REFL}}$

If **Vertical EHT Compensation** = -128 the outputs VD+ and VD- are independent of the input signal IBEAM.

## **Horizontal EHT Compensation**

This item controls the influence of the input signal IBEAM on the output E/W according to the following equation:

$$\Delta V_{\text{EW}} = \Delta V_{\text{IBEAM}} * \frac{\text{Horizontal EHT compensation} + 128}{128} * 2,12^{1})$$

$\Delta V_{\rm EW}$ : variation of E/W output voltage  $\Delta V_{\rm IBEAM}$ : variation of IBEAM input voltage

$^{1)}$  the factor 2.12 depends on  $V_{\mathsf{REFP}},\,V_{\mathsf{REFH}},\,V_{\mathsf{REFL}}$

If **Horizontal EHT Compensation** = -128 the output E/W is independent of the input signal IBEAM.

#### **AFC EHT Compensation**

Deviation of the horizontal phase caused by high beam current (e.g. white bar) can be eliminated by this control item. The beam current dependent input signal IBEAM is multiplied by **AFC EHT Compensation**.

Additional to the control items Vertical angle, Vertical bow and Horizontal shift, this product influences the horizontal phase at the output HD according to the following equation:

$$\Delta \phi = \Delta V_{\text{IBEAM}} * \frac{\text{AFC EHT compensation}}{64} * \frac{52^{1}}{\text{CLL}}$$

$\Delta \phi$ : variation of horizontal phase at the output HD

(positive values: shift left, negatives values: shift right)

$\Delta V_{\text{IRFAM}}$ : variation of IBEAM input voltage (units: Volt)

CLL:  $864 * f_{H}$

$^{1)}$  the factor 52 depends on  $V_{\mathsf{REFP}}$

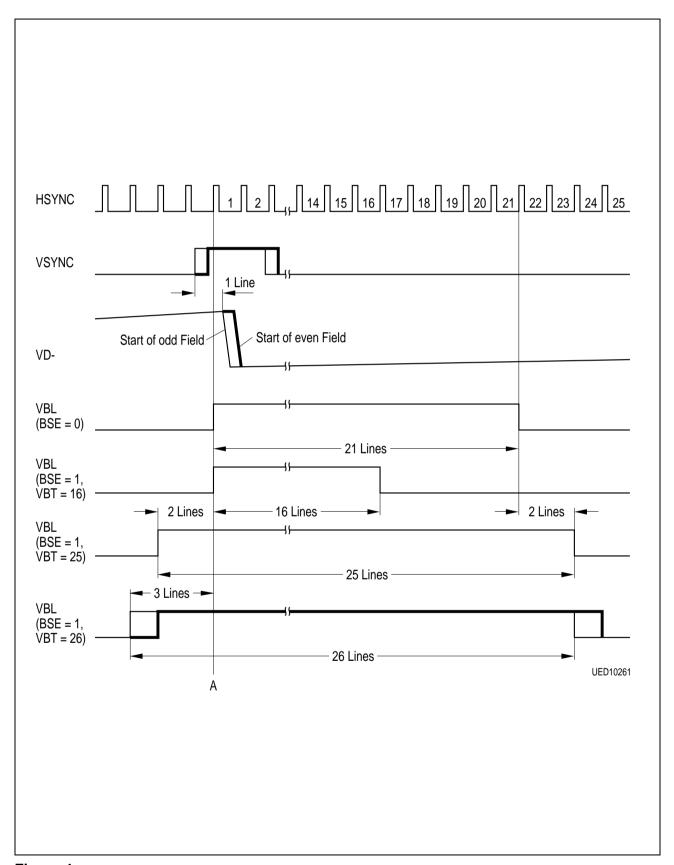

#### Vertical Blanking Time (VBT)

VBT defines the vertical blanking pulse VBL which is part of the output signal SCP. VBL is synchronized with the leading edge of HSYNC. It always starts and stops at the beginning of line and never in the center.

#### a) Case of STE = 0

In this case the control item Vertical blanking time defines the duration of the V-blanking pulse (VBL) exactly in number of lines. Because of IC internal limitations 16 through 127 lines can be blanked. If BSE = 0 the control item Vertical blanking time is disabled and always 21 lines (default value if disabled) are blank. After power on the control bit BSE is 0. Therefore 21 lines will be blanked before any programming of the IC. If **Vertical Blanking Time** is less or equals 21 lines, VBL starts (point A in fig. above) always 0 ... 0.5 line (new odd field) or 0.5 ... 1 line (new even field) prior to the vertical flyback. Otherwise VBL is concentric to a fictitious vertical flyback period of 21 lines, that means VBL starts (VBT - 21) / 2 lines at the end of an odd field or (VBT - 20) / 2 at the end of an even field prior to point A. Possible start points are only the beginning of line.

Figure 4

Vertical Blanking Pulse VBL when STE = 0 and Number of Lines per Field = Constant

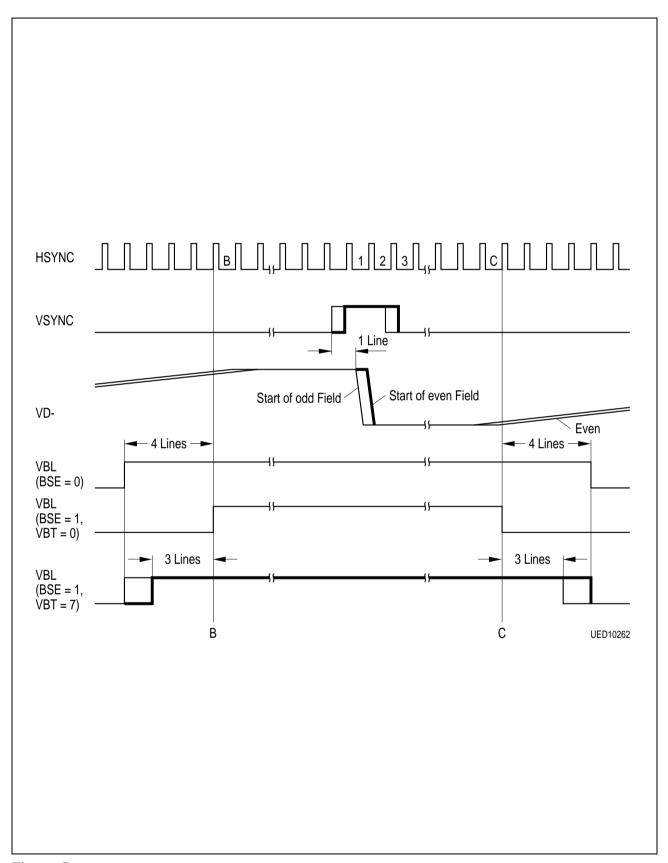

- b) Case of STE = 1

- In this case the control item Vertical blanking time is an extension for the V-blanking pulse.

- If BSE = 1 and VBT = 0 the V-blanking pulse has its minimum: it starts always at end of scan (line B in Fig. below) and ends at start of scan (line C) defined by the control items **Start Vertical Scan** (if SSE = 1) and **Vertical Scan**.

- BSE = 1 and (128 > VBT > 0) extend the V-blanking pulse according to the following relationship

(If VBT > 127 this value is ignored and replaced by VBT - 128): VBL starts VBT / 2 lines (even field) respectively (VBT + 1) / 2 lines (odd field) prior to line B.

VBL ends (VBT + 1) / 2 lines (even field) respectively VBT / 2 lines (odd field) after end of line C.

Possible start points are only the beginning of line.

- If BSE = 0 (after power on) the control item **Vertical Blanking Time** is disabled and VBL starts 4 lines prior to end of scan (line B) and ends 4 lines after start of scan (line C).

Figure 5

Vertical blanking pulse VBL when STE = 1

#### Minimum Number of Lines per Field

It defines the minimum number of lines per field for the vertical synchronisation. If the TV standard at the inputs VSYNC and HSYNC has less lines per field than defined by **Minimum Number of Lines per Field** no synchronisation is possible. The relationship between **Minimum Number of Lines per Field** and the minimum number of lines is given in the following table:

| Minimum Number of Lines per Field | Minimum Number of Lines per Field |

|-----------------------------------|-----------------------------------|

| 0                                 | 192                               |

| 1                                 | 194                               |

|                                   |                                   |

| 127                               | 446                               |

| 128                               | 448                               |

|                                   |                                   |

| 254                               | 700                               |

| 255                               | 702                               |

## **Maximum Number of Lines per Field**

It defines the maximum number of lines per field for the vertical synchronisation. If the TV standard at the inputs VSYNC and HSYNC has more lines per field than defined by **Maximum Number of Lines per Field** no synchronisation is possible. The relationship between **Maximum Number of Lines per Field** and the maximum number of lines is given in the following table:

| Maximum Number of Lines per Field | Maximum Number of Lines per Field |

|-----------------------------------|-----------------------------------|

| 0                                 | 702                               |

| 1                                 | 192                               |

| 2                                 | 194                               |

|                                   |                                   |

| 127                               | 444                               |

| 128                               | 446                               |

|                                   |                                   |

| 255                               | 700                               |

## **Most Important V-Deflection Modes for 4:3 CRT**

| Mode | Description                                                                                | Characteristics                                                                                                                                                                                                                                                    | Notes                                                                                                  | VR1<br>VR0 | NSA | SRSE | GBE | STE | SSE |

|------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------|-----|------|-----|-----|-----|

| N0   | Normal mode<br>(for 4:3 source,<br>Letterbox)<br>with <b>default</b><br>settings           | Self adaptation scan start = line 9 start of V-ramp = line 9 scan time: depends on source signal guard band = 1.5 lines                                                                                                                                            | Mode after power on                                                                                    | 00         | 0   | 0    | 0   | 0   | 0   |

| N1   | Normal mode<br>(for 4:3 source,<br>Letterbox)<br>with <b>user</b><br><b>defined</b> values | Self adaptation scan start = Start Vertical Scan if (Start Reduced Scan>Start Vertical Scan) start of V-ramp = Start Reduced Scan else start of V-ramp = Start Vertical Scan scan time: depends on source signal guard band = Guard Band/2 [lines]                 | Start of scan<br>adjustable<br>start of<br>V-ramp<br>adjustable<br>guard band<br>adjustable            | 00         | 0   | 1    | 1   | 0   | 1   |

| S0   | Shrink mode<br>75% (for 16:9<br>source)<br>with <b>default</b><br>settings                 | Self adaptation<br>scan start = line 9<br>start of reduced V-ramp = line 9<br>scan time: depends on source signal<br>guard band = 1.5 lines                                                                                                                        |                                                                                                        | 01         | 0   | 0    | 0   | 0   | 0   |

| S1   | Shrink mode<br>75% (for 16:9<br>source)<br>with <b>user</b><br><b>defined</b> values       | Self adaptation scan start = Start Vertical Scan if (Start Reduced Scan>Start Vertical Scan) start of reduced V-ramp = Start Reduced Scan else start of reduced V-ramp = Start Vertical Scan scan time: depends on source signal guard band = Guard Band/2 [lines] | Start of scan<br>adjustable<br>start of<br>reduced<br>V-ramp<br>adjustable<br>guard band<br>adjustable | 01         | 0   | 1    | 1   | 0   | 1   |

## **Most Important V-Deflection Modes for 16:9 CRT**

| Mode | Description                                                                     | Characteristics                                                                                                                                                                                                                                                     | Notes                                                                                                            | VR1<br>VR0 | NSA | SRSE | GBE | STE | SSE |

|------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------|-----|------|-----|-----|-----|

| N0   | ,                                                                               | Self adaptation scan start = line 9 start of V-ramp = line 9 scan time: depends on source signal guard band = 1.5 lines                                                                                                                                             | Mode after<br>power on                                                                                           | 00         | 0   | 0    | 0   | 0   | 0   |

| N1   | Normal mode<br>(for 16:9 or<br>4:3 source) with<br>user defined<br>values       | Self adaptation scan start = <b>Start Vertical Scan</b> if (Start reduced scan > Start vertical scan) start of V-ramp = Start reduced scan else start of V-ramp = Start vertical scan scan time: depends on source signal guard band = <b>Guard Band</b> /2 [lines] | Start of scan<br>adjustable<br>start of<br>V-ramp<br>adjustable<br>guard band<br>adjustable                      | 00         | 0   | 1    | 1   | 0   | 1   |

| Z    | Zoom mode<br>(for 4:3 source,<br>Letterbox)                                     | Scan start =    (number_of_lines - Vertical Scan)/2 +8 scan time = Vertical Scan                                                                                                                                                                                    | Vertical<br>scan<br>controls<br>zoom factor                                                                      | 00         | 0   | Х    | X   | 1   | 0   |

| SC   | Scroll mode<br>(for 4:3 source,<br>Letterbox)                                   | Scan start =   (number_of_lines - Vertical Scan)/2 +8 +   Start vertical scan scan time = Vertical Scan                                                                                                                                                             | Like above;<br>start<br>vertical scan<br>can be<br>additionally<br>used for<br>adjustment<br>of picture<br>phase | 00         | 0   | X    | X   | 1   | 1   |

| M    | Manual mode<br>(for 4:3 source,<br>Letterbox)                                   | Scan start = Start Vertical Scan<br>scan time = Vertical Scan                                                                                                                                                                                                       | Scan start<br>and scan<br>time are<br>separately<br>adjustable                                                   | 00         | 1   | Х    | X   | 1   | X   |

| S2   | Shrink mode<br>66% (for two<br>4:3 sources)<br>with <b>default</b><br>settings  | Self adaptation scan start = line 9 start of reduced V-ramp = line 9 scan time: depends on source signal guard band =1.5 lines                                                                                                                                      |                                                                                                                  | 10         | 0   | 0    | 0   | 0   | 0   |

| S3   | Shrink mode<br>50% (for two<br>16:9 sources)<br>with <b>default</b><br>settings | Self adaptation scan start = line 9 start of reduced V-ramp = line 9 scan time: depends on source signal guard band = 1.5 lines                                                                                                                                     |                                                                                                                  | 11         | 0   | 0    | 0   | 0   | 0   |

#### 3 Absolute Maximum Ratings

| Parameter                          | Symbol       | Limit '                 | Values               | Unit | Remark             |

|------------------------------------|--------------|-------------------------|----------------------|------|--------------------|

|                                    |              | min.                    | max.                 |      |                    |

| Operating temperature              | $T_{A}$      | -20                     | 70                   | °C   |                    |

| Storage temperature                | $T_{ m stg}$ | -40                     | 125                  | °C   |                    |

| Junction temperature               | $T_{j}$      |                         | 125                  | °C   |                    |

| Soldering temperature              | $T_{S}$      |                         | 260                  | °C   |                    |

| Input voltage                      | $V_{I}$      | V <sub>SS</sub> - 0.3 V | $V_{\rm DD}$ + 0.3 V |      |                    |

| Output voltage                     | $V_{Q}$      | V <sub>SS</sub> - 0.3 V | $V_{\rm DD}$ + 0.3 V |      |                    |

| Supply voltages                    | $V_{DD}$     | -0.3                    | 6                    | V    |                    |

| Supply total voltage differentials |              | -0.25                   | 0.25                 | V    | 1)                 |

| Total power dissipation            | $P_{tot}$    |                         | 0.85                 | W    |                    |

| Latch-up protection                |              | -100                    | 100                  | mA   | All inputs/outputs |

Between any internally non-connected supply pin of the same kind. All  $V_{\text{DD(D)}}$  - and  $V_{\text{DD(A)}}$  - Pins are connected internally by about 3  $\Omega$  The  $V_{\text{SS(D)}}$  - Pins are connected internally by about 3  $\Omega$

**Note**: Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions or at any other condition beyond those indicated in the operational sections of this specification is not implied.

## 3.1 Recommended Operating Conditions

| Parameter                           | Symbol      | L        | imit Val | ues      | Unit    | Remark                           |

|-------------------------------------|-------------|----------|----------|----------|---------|----------------------------------|

|                                     |             | min.     | nom.     | max.     |         |                                  |

| Supply voltages                     | $V_{DD}$    | 4.5      | 5        | 5.5      | V       |                                  |

| Ambient temperature                 | $T_{A}$     | -20      | 25       | 70       | °C      | For analog parameters 0°C        |

| TTL Inputs: CLL, HS                 | YNC, VSY    | NC, TE   | ST, SSI  | , HDED   | EF, RE  | SN                               |

| H-input voltage                     | $V_{IH}$    | 2.0      |          | $V_{DD}$ | V       |                                  |

| L-input voltage                     | $V_{IL}$    | 0        |          | 0.8      | V       |                                  |

| Input VPROT                         |             | •        |          | •        | 1       | •                                |

| Threshold V1                        |             | 1.4      | 1.5      | 1.6      | V       | $V_{REFP}$ = 4 V                 |

| Threshold V2                        |             | 0.9      | 1.0      | 1.1      | V       | $V_{REFP}$ = 4 V                 |

| Input HPROT                         | •           | 1        | l        | 1        | ı       | •                                |

| Threshold V1                        |             | 3.9      | 4        | 4.1      | V       | $V_{REFP}$ = 4 V                 |

| Threshold V2                        |             | 2.1      | 2.4      | 2.7      | V       | $V_{REFP} = 4 \; V$              |

| Input IBEAM                         | 1           | <b>J</b> | <u>'</u> | 1        | II.     |                                  |

| L-input voltage                     | $V_{IL}$    |          | 2        |          | V       | $V_{REFP} = 4 \; V$              |

| Full range input voltage            |             |          | 3        |          | V       | $V_{REFP}$ = 4 V                 |

| Reference Voltage Inp               | out Pins (I | nternal  | Voltage  | Ref Con  | trol By | te Reg 48 <sub>H</sub> = 0000001 |

| $\overline{V_{REFP}}$ input voltage | $V_{VREFP}$ |          | 4        |          | V       |                                  |

| $\overline{V_{REFH}}$ input voltage | $V_{VREFH}$ |          | 2.5      |          | V       |                                  |

| $V_{REFL}$ input voltage            | $V_{VREFL}$ |          | 1.2      |          | V       |                                  |

| $V_{REFN}$ input voltage            | $V_{VREFN}$ |          | 0        |          | V       |                                  |

| Input ⊕2                            | 1           | <b>J</b> | <u>'</u> | 1        | II.     |                                  |

| L-input voltage                     | $V_{IL}$    | 0        |          | 0.7      | V       | $V_{REFP} = 4 \; V$              |

| H-input voltage                     | $V_{IH}$    | 2.0      |          | $V_{DD}$ | V       | $V_{REFP}$ = 4 V                 |

| Input HSYNC                         | 1           |          | L        |          | 1       | •                                |

| Pulse width high                    |             | 100      |          | 20000    | ns      |                                  |

| Setup time                          | $t_{SU}$    | 7        |          |          | ns      |                                  |

| Hold time                           | $t_{H}$     | 6        |          |          | ns      |                                  |

| Input capacitance                   | $C_{I}$     | 1        |          | 10       | pF      |                                  |

## 3.1 Recommended Operating Conditions (cont'd)

| Parameter                          | Symbol        | Li                 | mit Val     | ues                | Unit        | Remark                      |

|------------------------------------|---------------|--------------------|-------------|--------------------|-------------|-----------------------------|

|                                    |               | min.               | nom.        | max.               |             |                             |

| Input VSYNC                        |               |                    |             |                    |             |                             |

| Pulse width high                   |               | 100                |             | 100/f <sub>H</sub> | ns          | NI = 0                      |

| Pulse width high                   |               | 1.5/f <sub>H</sub> |             | 100/f <sub>H</sub> |             | NI = 1                      |

| Input capacitance                  | $C_{I}$       |                    |             | 10                 | pF          |                             |

| Input CLL                          |               | •                  |             |                    |             | •                           |

| Input frequency                    | $f_{I}$       | 25                 | 27          | 30                 | MHz         |                             |

| Input capacitance                  | $C_{I}$       |                    |             | 10                 | pF          |                             |

| Quartz Oscillator Inp              | ut / Outpu    | ıt X1, X           | 2           | ·                  |             | •                           |

| Crystal frequency                  |               |                    | 12          |                    | MHz         | Fundamental crystal type    |

| Crystal resonant impedance         |               |                    |             | 25                 | Ω           |                             |

| External capacitance               |               |                    | 27          |                    | pF          | See application information |

| I <sup>2</sup> C Bus (All Values a | re Referre    | ed to m            | $in.(V_IH)$ | and ma             | $x.(V_IL))$ |                             |

| H-input voltage                    | $V_{IH}$      | 3                  |             | $V_{DD}$           | V           |                             |

| L-input voltage                    | $V_{IL}$      | 0                  |             | 1.5                | V           |                             |

| SCL clock frequency                | $f_{\sf SCL}$ | 0                  |             | 400                | kHz         |                             |

| Rise times of SCL,<br>SDA          | $t_{R}$       |                    |             | 0.3                | μs          | $f_{\rm SCL}$ = 400 kHz     |

| Fall times of SCL,<br>SDA          | $t_{F}$       |                    |             | 0.3                | μs          |                             |

| Set-up time DATA                   | $t_{SU;DA}$   | 100                |             |                    | ns          |                             |

| Hold time DATA                     | $t_{HD;DA}$   | 0                  |             |                    | ns          |                             |

| Load capacitance                   | $C_{L}$       |                    |             | 400                | pF          |                             |

## 3.2 Characteristics (Assuming Recommended Operating Conditions)

| Parameter                | Symbol       | Liı                           | mit Valu            | ies                           | Unit | Remark                                      |

|--------------------------|--------------|-------------------------------|---------------------|-------------------------------|------|---------------------------------------------|

|                          |              | min.                          | nom.                | max.                          |      |                                             |

| Average supply current   | $I_{\rm CC}$ |                               | 50                  | 100                           | mA   |                                             |

| Standby supply current   |              |                               |                     | 25                            | mA   |                                             |

| <b>Output Pins: VBLE</b> | , SW1, SW2   | 2                             | 1                   |                               | •    |                                             |

| Output low level         | $V_{OL}$     |                               |                     | 0.4                           | V    | $I_{\rm O}$ = 1 mA                          |

| Output high level        | $V_{OH}$     | 2.8                           |                     |                               | V    | $I_{\rm O}$ = -1 mA                         |

| Input / Output SDA       |              |                               |                     |                               |      | •                                           |

| Output low level         | $V_{OL}$     |                               |                     | 0.6                           | V    | $I_{\rm O}$ = 6 mA                          |

| Output SCP               |              |                               |                     |                               |      | •                                           |

| Output low level         | $V_{OL}$     | 0                             |                     | 1                             | V    | $I_{\rm O}$ = 1 mA                          |

| Output HBL level         | $V_{OHBL}$   | V <sub>DD</sub> / 2<br>-0.4 V | V <sub>DD</sub> / 2 | V <sub>DD</sub> / 2<br>+0.4 V |      | I <sub>O</sub>   = 100 μA                   |

| Output high level        | $V_{OH}$     | 4.0                           |                     | $V_{DD}$                      | V    | $I_{\rm O}$ = -1 mA                         |

| DAC Output E/W           |              | -1                            | 1                   |                               | •    |                                             |

| DAC resolution           |              |                               | 10                  |                               | Bit  | Linear range:<br>100 900                    |

| DAC output low           |              |                               | 1.45                |                               | V    | Input data = 100 <sup>1)</sup>              |

| DAC output high          |              |                               | 3.48                |                               | V    | Input data = 900 <sup>1)</sup>              |

| Load capacitance         | $C_{L}$      |                               |                     | 30                            | pF   |                                             |

| Output load              |              | 20                            |                     |                               | kΩ   |                                             |

| Zero error               |              | -2 %                          |                     | 2 %                           |      | DAC output<br>voltage = 2.5 V <sup>2)</sup> |

| Gain error               |              | -5 %                          |                     | 5 %                           |      | 2)                                          |

| INL                      |              | -0.2 %                        |                     | 0.2 %                         |      | 2)                                          |

| DNL                      |              | -0.1 %                        |                     | 0.1 %                         |      | 2)                                          |

<sup>1)</sup>  $V_{\text{REFH}}$  = 2.5 V,  $V_{\text{REFL}}$  = 1.2 V

$<sup>^{2)}</sup>$   $V_{\rm REFH}$  = 2.5 V,  $V_{\rm REFL}$  = 1.2 V, Input range = 100 ... 900

#### 3.2 Characteristics (Assuming Recommended Operating Conditions) (cont'd)

| Parameter                       | Symbol  | Limit Values |       | Unit  | Remark |                                  |  |  |  |  |

|---------------------------------|---------|--------------|-------|-------|--------|----------------------------------|--|--|--|--|

|                                 |         | min.         | nom.  | max.  |        |                                  |  |  |  |  |

| DAC Output VD+, VD-             |         |              |       |       |        |                                  |  |  |  |  |

| DAC resolution                  |         |              | 14    |       | Bit    | Linear range:<br>1500 15000      |  |  |  |  |

| DAC output low (VD-)            |         |              | 1.44  |       | V      | Input data = 1500 <sup>1)</sup>  |  |  |  |  |

| DAC output high (VD-)           |         |              | 3.58  |       | V      | Input data = 15000 <sup>1)</sup> |  |  |  |  |

| DAC output low<br>(VD-) - (VD+) |         |              | -2.12 |       | V      | Input data = 1500 <sup>1)</sup>  |  |  |  |  |

| DAC output high (VD-) - (VD+)   |         |              | 2.16  |       | V      | Input data = 15000 <sup>1)</sup> |  |  |  |  |

| Load capacitance                | $C_{L}$ |              |       | 30    | pF     |                                  |  |  |  |  |

| Output load                     |         | 20           |       |       | kΩ     |                                  |  |  |  |  |

| Zero error                      |         | -1 %         |       | 1 %   |        | $(VD-) - (VD+) = 0 V^{2)}$       |  |  |  |  |

| Gain error                      |         | -5 %         |       | 5 %   |        | 2)                               |  |  |  |  |

| INL                             |         | -0.5 %       |       | 0.5 % |        | 2)                               |  |  |  |  |

| DNL                             |         | Monoto       | nous  | •     |        | Guar. by design                  |  |  |  |  |

<sup>&</sup>lt;sup>1)</sup>  $V_{\text{REFH}}$  = 2.5 V,  $V_{\text{REFL}}$  = 1.2 V

#### Reference Output $V_{\mathsf{REFP}}$ (Adjust. by Reg $48_{H}$ , Bit D7 ... D2) (Reg $48_{H}$ , Bit D1 = 0, Bit D0 = 0) V 4.0 Bit D7 ... D2 = 100000 Output voltage min V Output voltage max 4.0 Bit D7 ... D2 = 011111 -50 0 Output current $I_{\mathsf{Q}}$ μΑ Reference Output $V_{\text{REFH}}$ (Reg 48<sub>H</sub>, Bit D1 = 0) $\overline{V}_{\mathsf{Q}}$ 2.4 2.5 2.6 V $V_{\mathsf{REFP}} = 4 \ \mathsf{V}$ Output voltage Reference Output $V_{\text{REFL}}$ (Reg 48<sub>H</sub>, Bit D1 = 0) $V_{\mathsf{Q}}$ 1.1 1.3 $V_{\mathsf{REFP}} = 4 \; \mathsf{V}$ Output voltage 1.2 **Output HD** V Output low level $V_{\mathsf{OI}}$ 0 $I_{\rm O}$ = 8 mA $V_{\mathsf{DD}}$ $V_{\mathsf{OH}}$ $V_{\mathsf{DD}}$ $I_0 = -8 \text{ mA}$ Output high level -1 V

<sup>&</sup>lt;sup>2)</sup>  $V_{REFH} = 2.5 \text{ V}, V_{REFL} = 1.2 \text{ V}, \text{ Input range} = 1500 ... 15000$

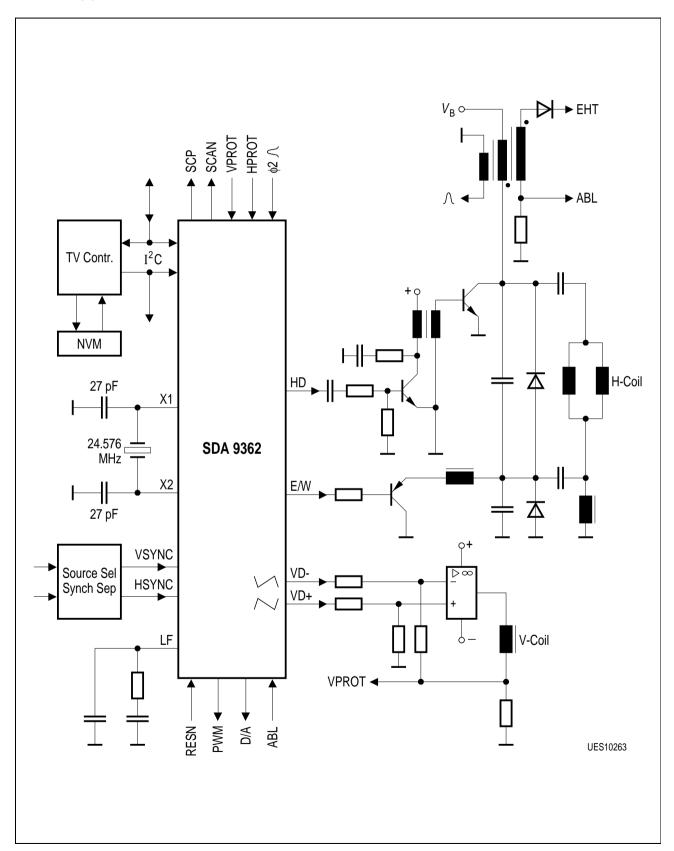

## 4 Application Information

Figure 6

## 5 Waveforms

## 5.1 VD- Output Voltage, 4/3-CRT and 16/9-Source

Figure 7

## 5.2 Function of H,V Protection

|   | HPROT    | VPROT             | Mode                                        | SCP                                        | HPON <sup>2)</sup><br>I <sup>2</sup> C Bus | VPON <sup>2)</sup><br>I <sup>2</sup> C Bus |

|---|----------|-------------------|---------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|

| 1 | V1<br>V2 |                   | Start up                                    | Continuous<br>blanking                     | 0                                          | 0                                          |

| 2 |          | V1                | H, V<br>operation                           | 1)                                         | 0                                          | 0                                          |

| 3 |          |                   | EHT over-<br>voltage                        | Continuous blanking after $t_2$            | 1<br>after $t_2$                           | 0                                          |

| 4 | or       | $t_0 < t \le t_1$ | H operation<br>V short<br>failure           | Continuous blanking after $t_0$ if SSC = 0 | 0                                          | 0                                          |

| 5 |          |                   | V longer<br>failure<br>H off<br>after $t_1$ | Continuous blanking after $t_0$ if SSC = 0 | 0                                          | 1<br>after t <sub>1</sub>                  |

| 6 | AAA      |                   | EHT<br>short over-<br>voltage               | Continuous blanking after $t_2$            | 1<br>after $t_2$                           | 1<br>after t <sub>1</sub>                  |

$$t_0 = 2 / f_v \dots 3 / f_v$$

$t_1 = 64 / f_v \dots 128 / f_v$   $t_2 = 1 / f_v \dots 2 / f_v$

$<sup>^{1)}</sup>$  Depends on  $I^2$ C-control items

$<sup>^{2)}</sup>$  HPON or VPON = 1:HD = 0 (OFF)

#### 5.3 Power On/Off Diagram

Figure 8

#### 5.4 Standby Mode, RESN Diagram

Figure 9

#### 6 Package Outlines

Figure 10

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device Dimensions in mm